Описание

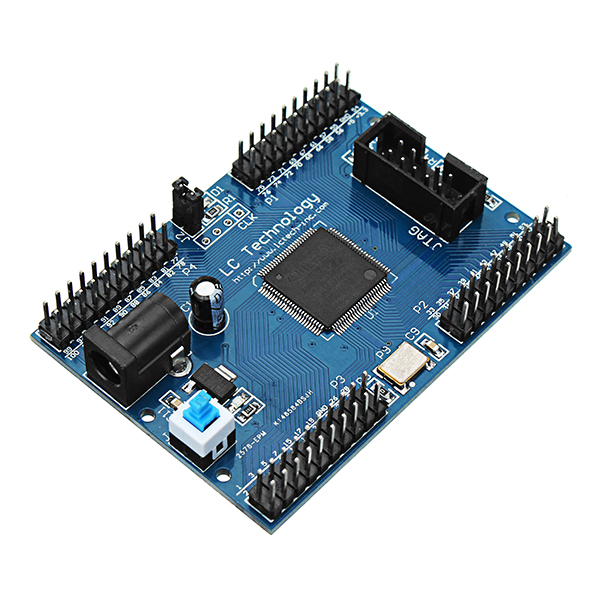

Altera MAX II EPM240 CPLD Development Board

EPM240 это самый начальный/дешевый из семейства MAX II чипов. А само семейство MAX II — это самое дешевое/простое семейство чипов ALTERA.

Внутри всего 240 LE (логических блоков). Что такое «логически блок» — это один триггер и несколько элементов и-не вокруг него, которые могут по всякому конфигурироваться при помощи данных, записанных в EEPROM.

И таки да! EPM240 это не FPGA. Эта микросхема является CPLD. Основное отличие CPLD от FPGA — в типе памяти, в котором хранится программа. В FPGA это SDRAM. В CPLD это EEPROM или FLASH. Для FPGA обязательно требуется внешнее хранилище программы. CPLD сразу после reset начинает работать. Так что CPLD довольно удобен, если твоя программа — статическая.

240 LE — много это или мало? Смотря для чего. Чтобы сэмулировать процессор — это мало. Чтобы сделать несколько счетчиков инкрементирующих — достаточно с огромным запасом.

Чтобы сделать 16-ти битный регистр для данных нужно 16 LE.

Чтобы сделать 16-ти битный инкрементальный счетчик тоже 16 LE.

Еще один плюс подобной микросхемы — это большое количество ножек на корпусе и возможность достаточно свободно указывать какие ножки для чего использовать. Корпус LQFP100 и большая часть ножек работает для input/output. Кто решал головоломку с одновременным использованием SPI/UART/FSMC/I2S на STM32, тот знает какой это геморрой.

Отзывы

Отзывов пока нет.